HP 82941A

# **BCD** Interface

**OWNER'S MANUAL**

**SERIES 80**

# HP82941A BCD Interface

Owner's Manual

Series 80

$\bf April\ 1982$

Reorder Number 82941-90011

#### Section 1

# **General Information**

#### Introduction

The HP 82941A BCD Interface provides the HP Series 80 Personal Computers with the capability of interfacing up to two peripheral instruments that handle numeric information in BCD (binary coded decimal) form. These instruments fall into a variety of classifications including voltmeters, multimeters, counters, and any peripheral that outputs and/or inputs BCD information.

This manual provides general information about the interface, how to install it and a guide to programming to provide the best use of the interface features.

#### I/O ROM

To operate the interface, the I/O ROM (P/N 00085-15003 for the HP-85 and HP-83 or P/N 00087-15003 for the HP-87) is required. This ROM fits into a ROM drawer which plugs into any of the four I/O ports in the back of the computer.

# **Specifications**

Pertinent specifications are given in this section.

## **Power Requirements**

The computer supplies all power for the interface.

#### **Operating Temperature**

0°C to 55°C (32°F to 131°F)

#### Logic Requirements

Positive true or negative true logic may be used. The logic configuration may be set by switches on the interface circuit board or by software.

# Level Requirements

Input low: .8V @ 1mA.

Output low: .45V @ 4.5 mA.

Input high: 2.0V.

Output high:  $2.4V @ 240 \mu A$ .

#### I/O Data Lines

44 bi-directional lines via eleven 4-bit ports (P0 through P10.)

## Sign Bits

Four sign bits (S1 through S4) via port P11.

#### **Handshake Lines**

Four output lines (I/OA, I/OB, CTLA, CTLB). Two input lines (FLGA, FLGB).

#### Standard Data Format

The interface can recognize sixteen different BCD characters and two signs from the BCD bus. These are listed in table 1-1.

**BCD Code** Signs Positive Negative Positive Negative Representation Representation **True Logic True Logic** True Logic **True Logic** 0000 1111 0 0001 1110 0 0010 1101 2 0011 1100 3 0100 1011 4 0101 1010 5 0110 1001 6 1000 0111 7 1000 0111 8 1001 0110 1010 0101 : (colon) ; (semicolon) 1011 0100 1100 0011 < (less than) 1101 0010 = (equals) 0001 1110 >(greater than) 1111 0000 ? (question mark)

Table 1-1. BCD Characters

During an output, the interface accepts an ASCII code from the computer and outputs the lower four bits of this code to the BCD bus. However, ASCII codes 0 through 32, and code 44 are ignored by the interface.

#### Cable

The interface is supplied with a 31-conductor shielded cable connected to the interface on both ends. The cable is approximately 4 meters long. The cable structure is discussed in detail in section 2.

## **Dimensions**

Approximately  $16.7 \times 12.7 \times 1.5$  cm  $(6.59 \times 5 \times .59$  in).

# Installation

# **Unpacking and Inspection**

If the shipping carton is damaged, ask the carrier's agent to be present when the interface is unpacked. If the interface is damaged or fails to meet electrical specifications, immediately notify the carrier and the nearest HP sales and service office. Retain the shipping carton for the carrier's inspection. The sales and service office will arrange for the repair or replacement of your interface without waiting for the claim against the carrier to be settled.

# **Installation Considerations**

Standard terms for BCD lines have not been adopted by different manufactures of BCD devices. In some cases you may need to know the purpose a line serves to know where to terminate it on a peripheral. The following installation options should be read and understood before installation is attempted.

The select code and default configuration switches may be set to meet the needs of your installation, or, many of the interface modes can be configured by software.

The switches are preset at the factory as follows:

- Select Code 3.

- Standard Format (1 channel).

- Trailing Edge Handshake.

- Positive True Logic On All Data Lines, Port 10, Port 11 (Sign Bits).

- Outputs Disabled.

The select code and output disabled are the two switch configurations that cannot be re-configured by software. These two items must be configured by the switches. Software can re-configure the interface and ignore the remaining switch settings.

If you wish to verify or change any of the above switch settings, refer to the following disassembly procedure and disassemble the interface. Then refer to the discussion of the switch settings. If this isn't necessary, refer to the discussion of the interface cable on page 00.

# Disassembly

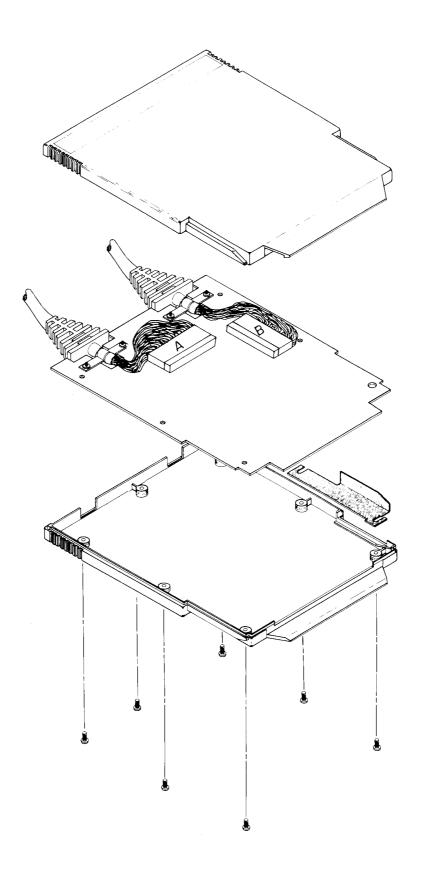

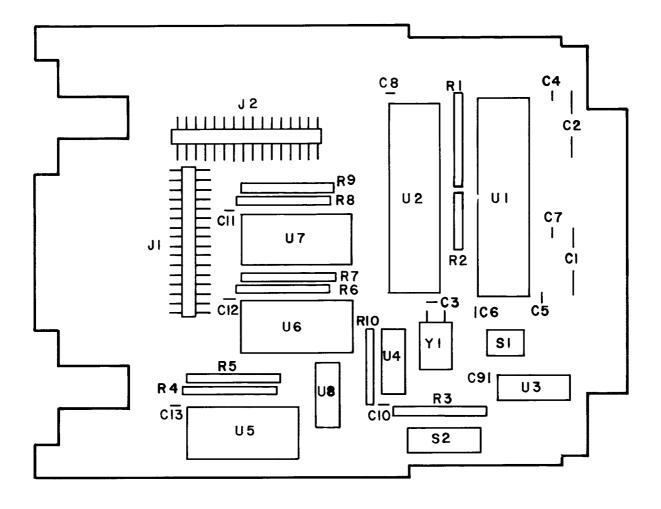

Refer to figure 2-1 to see how the interface parts fit together. Place the interface on a flat surface with the side having the seven screws facing upward and the cable coming out to the left. Then use the following steps to disassemble the interface:

- 1. Use a Pozidriv® screwdriver and remove the screws.

- 2. Hold the interface parts together and turn the interface over so that the seven screw holes are facing downward and the cable is coming out to the left.

- 3. Hold the cable strain reliefs in place and remove the top half of the interface housing.

If you have followed the above steps, the switches should be oriented as shown in the following figures. If they are not, orient the switches as shown before identifying the switch segments.

After the switches are set to meet your needs, refer to the discussion on cables before you reassemble the interface since it may be necessary to remove one end of the cable from the interface.

To reassemble the interface, reverse the above procedure, making sure the ground contact is in place. The ground contact should be under the circuit board when the component side is up.

Figure 2-1. Disassembly

## **Switch Settings**

As previously noted, the select code and default configuration switches are preset at the factory. Once the interface is disassembled, any of the factory settings may be changed or verified by referring to the following discussions of these functions.

The interface may be equipped with either slide or rocker type switches. Both types are illustrated in the factory preset positions.

Note: If you change any of the factory settings, make sure that you change the proper switch segments. Do not disturb the settings of adjoining switches. The small tip of a pencil or similar object is recommended for this purpose.

#### **Select Code Switches**

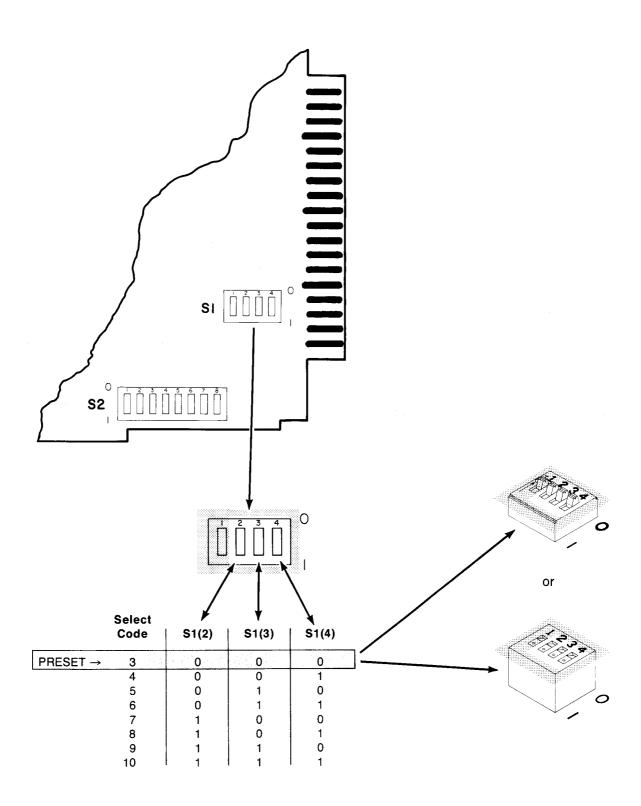

Switch segments 2, 3 and 4 of switch S1 are preset at the factory for select code 3 as follows:

- Switch segment 2 set to "0".

- Switch segment 3 set to "0".

- Switch segment 4 set to "0".

- Switch segment 1 is not used and may be in either position.

The "0" and "1" positions are labeled on the circuit board.

Select codes 3 through 10 may be set with these switch segments. To change or verify the factory settings, orient the circuit board as shown in figure 2-2 and locate switch segments 2, 3 and 4 of switch S1. Then identify the "0" and "1" switch positions on the circuit board. You may verify that select code 3 is properly set by comparing the actual positions of switch segments 2, 3 and 4 with those illustrated. They should be the same.

To change the select code, refer to the table of figure 2-2 and set switch segments 2, 3 and 4 as required for the select code chosen. For example, if select code 10 is to be set, the three switch segments must all be set to "1". In this case, if the switches are the slide type, slides 2, 3 and 4 must all be set to the "1" position; if they are the rocker type, all three rockers must be pressed down toward the "1" position.

Note: Select codes 1 and 2 are reserved for the CRT and (internal) printer, respectively.

Figure 2-2. Select Code Switches

# **Default Configuration Switches**

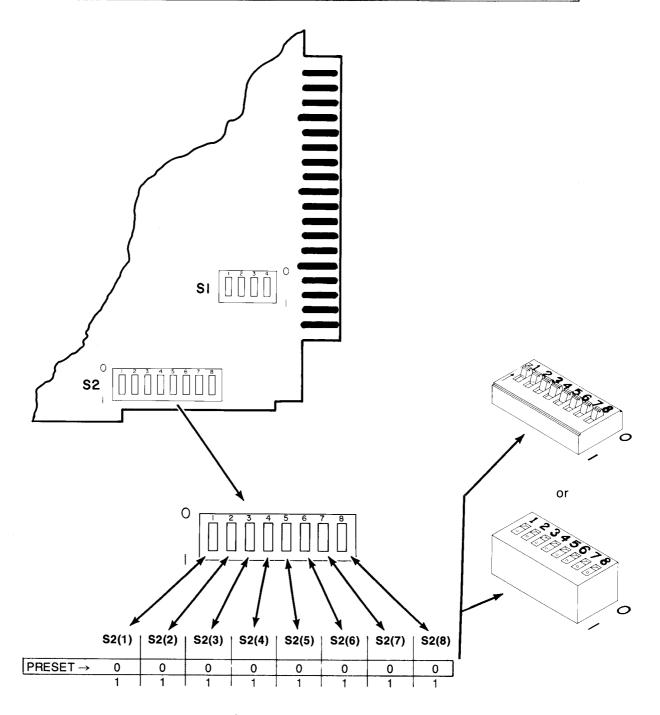

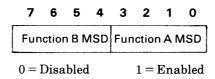

Switch segments 1 through 8 of switch S2 are all preset to "0" at the factory to implement the following:

- Standard Format (1 channel)

- Trailing-edge Handshake

- Positive True Logic for Data Lines

Sign Bits

D . 10

Port 10

Control Lines

Flag Lines

• Output Disabled (software cannot re-configure this function)

The "0" and "1" switch positions are labeled on the circuit board.

To verify any of the factory settings, orient the circuit board as shown in figure 2-3 and locate switch S2. Then identify the "0" and "1" switch positions on the circuit board. The factory settings should have switch segments 1 through 8 in the "0" positions as illustrated.

To change any of the factory settings, refer to the table of figure 2-3 and identify the switch segments you wish to change. For example, if you want to enable outputs, you must set switch segment 8 to the "1" position. Any of the configuration switches may be changed to meet your needs. However, keep in mind that software can ignore any of the switch settings except switch segment 8 and the select code switches.

| Switch<br>Segment | Assignment      | Set to ''0''                | Set to "1"                 |

|-------------------|-----------------|-----------------------------|----------------------------|

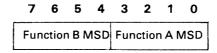

| S2(1)             | Format          | Standard Format (1 channel) | Option Format (2 channels) |

| S2(2)             | Handshake Lines | Trailing Edge               | Leading Edge               |

| S2(3)             | Data Sense      | Positive True Logic         | Negative True Logic        |

| S2(4)             | Signs Sense     | Positive True Logic         | Negative True Logic        |

| S2(5)             | Port 10 Sense   | Positive True Logic         | Negative True Logic        |

| S2(6)             | Control Sense   | Positive True Logic         | Negative True Logic        |

| S2(7)             | Flag Sense      | Positive True Logic         | Negative True Logic        |

| S2(8)             | Output Enable   | Outputs Disabled            | Outputs Enabled            |

Figure 2-3. Default Switches

# **Interface Cable**

This discussion will assist you in cutting the interface cable to the proper length, identifying the cable contents and preparing the cable ends.

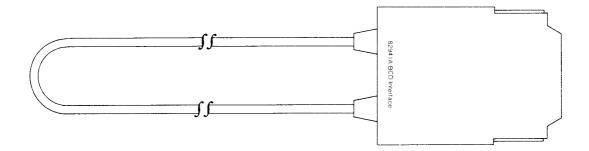

The interface is delivered with a single 31-conductor shielded cable, 4 meters long. Each end of the cable is terminated to the interface circuit board by plug-in connectors as illustrated in figure 2-4.

Figure 2-4. Interface Cable Before Cutting

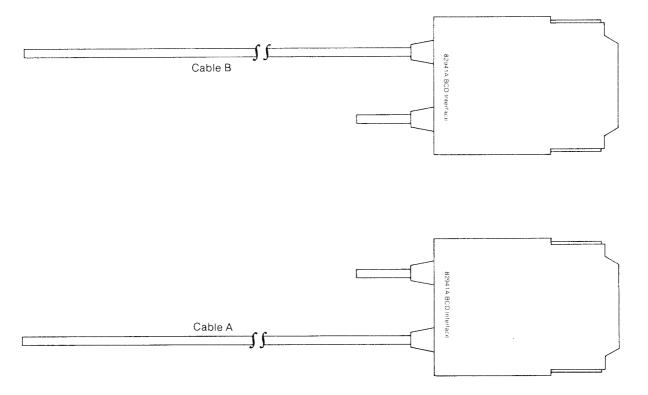

The cable must be cut to interface a peripheral. If it is cut very near one end, you will have one cable approximately 4 meters long. This single cable could be cable A or cable B, depending upon which end is cut as illustrated in figure 2-5. Generally, a single cable interfaces one peripheral. However, it is possible to interface two peripherals with one cable or one peripheral with both cables.

Figure 2-5. Single Cable Configurations

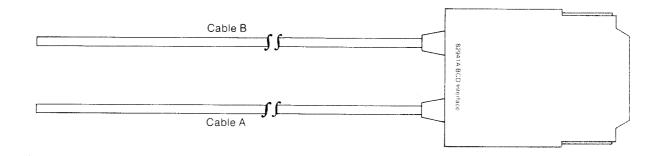

If the cable is cut in the center, you will have two cables, each 2 meters long as illustrated in figure 2-6. In a 2-cable configuration, various lengths for each cable may be obtained by cutting the supplied cable at intermediate points between one end and it's center. Two cables can interface two peripherals or one peripheral with extended digit capability.

Figure 2-6. Two Cable Configuration

If you require two cables and the length of each must be more than 2 meters, order another cable by specifying HP part number 8120-3192. Then, remove either end of the supplied cable by removing the cable clamp hardware and unplugging the cable connector from the circuit board. Plug the new cable onto the circuit board connector and secure with the cable clamp hardware. This will provide you with two cables that can be cut to a length of up to 4 meters each. Cables longer than 4 meters should not be used.

If two peripherals are to be interfaced and one requires more digit capability than one cable can provide, it is permissible to split one cable between two devices.

As you can see, there are several considerations that need to be made before you cut the cable. Once you decide where to cut it, use a pair of wire cutters large enough to accommodate the cable diameter.

#### **CAUTION**

If the cable is cut so that there is only one cable, the unused cable stub should be removed from the circuit board. If the cable stub is left connected and any of the wires become shorted together or come in contact with a conductive surface during I/O operations, equipment damage may result. After the interface is reassembled, use a piece of electrical tape to cover the hole resulting from the removal of the unused cable stub.

#### Cable Structure/Default Formats

Let's now examine the contents of each cable. Wire colors of the various lines are given later.

Cable A contains the following BCD lines:

BCD Ports P0 — P4 (4 bits each)

BCD Port P10 (4 bits)

Sign Bits S1 and S2 (1/2 of P11)

I/OA (1 bit)

CTLA (1 bit)

FLGA (1 bit)

GND (2 lines)

A and B Shield

Cable B contains the following BCD lines:

BCD Ports P5 — P9 (4 bits each)

BCD Port P10 (4 bits)

Sign Bits S3 and S4 (1/2 of P11)

I/OB(1 bit)

CTLB (1 bit)

FLGB (1 bit)

GND

A and B Shield

Notice that ports P0 through P4 are in cable A while cable B continues with ports P5 through P9. Also notice that port P10, plus the GND and shield wires for both channels are in both cables. Let's look at this two-cable port structure more closely.

Ports P0 through P10 may be used to transfer mantissa, exponent or function digits that were listed in table 1-1. One or two peripherals may be connected to these ports. The number of ports used by a peripheral is determined by its functional capability and/or the amount of resolution needed. Thus, one peripheral may use one port or, by using both cables, all of the ports.

Switch segment 1 of switch S2 selects one of two default formats or the interface can be configured by software. If a switch settable default format is used, the various ports have dedicated assignments as shown in tables 2-1 and 2-2. However, by writing to the appropriate registers given in section 3, the port assignments can be changed in a variety of ways and thereby ignore the switch settings.

Table 2-1. Standard Default Format (one peripheral)

| Number<br>Input/Output<br>Ports | Ports/Bits Used | Digit<br>Representation | Handshake<br>Lines Used |

|---------------------------------|-----------------|-------------------------|-------------------------|

| 8                               | PO — P7         | Mantissa                | Channel A               |

| 1                               | P8              | Exponent                | Channel A               |

| 1                               | P9              | Function                | Channel A               |

| 1/2                             | P11 (S1, S2)    | Signs                   | Channel A               |

Note: Channel A handshake lines include I/OA, CTLA and FLGA.

Table 2-2. Option Default Format (two peripherals)

| Number of<br>Input/Output<br>Ports | Ports/Bits Used | Digit<br>Representation | Handshake<br>Lines Used |

|------------------------------------|-----------------|-------------------------|-------------------------|

| 4                                  | P0 — P3         | Mantissa                | Channel A               |

| 1                                  | P4              | Function                | Channel A               |

| 4                                  | P5 — P8         | Mantissa                | Channel B               |

| 1                                  | P9              | Function                | Channel B               |

| 1/2                                | P11 (S1, S2)    | Signs                   | Channel A               |

| 1/2                                | P11 (S3, S4)    | Signs                   | Channel B               |

Note: Channel A handshake lines include I/OA, CTLA and FLGA; channel B handshake lines include I/OB, CTLB and FLGB.

Notice that the exponent field is not used in the option default format. However, it may be used if the interface is configured by software. In fact, you can specify as many as three exponent digits per channel with a software configuration. Also notice that neither of the switch settable default formats use port P10 directly. This port is also accessed by software and is useful as a control port.

Notice that the ports are assigned in consecutive order from the mantissa, exponent and function fields. For example, the standard default format uses ports P0 through P7 for the mantissa digits with P0 representing the most significant; port P8 is used for the exponent; port P9 is used for the function. If this format is used, all of these ports will have these dedicated assignments and be used in a transfer, even if nothing has been wired to a port. Therefore, if you don't need eight digit mantissa resolution or, perhaps exponent and/or function digits aren't needed at all, you will most likely want to re-configure the interface by software.

The option default format also uses dedicated port assignments as outlined in table 2-2. Notice that exponent digits are not used in this format. If this format is used, one peripheral is terminated to cable A and one peripheral is terminated to cable B. If you are going to interface two peripherals and this format will not fulfill your needs, again the interface can be configured by software.

Since the switch settable formats will not satisfy all installation requirements, let's briefly consider a software configuration. This will be discussed in more detail later. For now, let's consider the restrictions. Any configuration is legal if the following restrictions are observed:

- 1. The sum of all ports used must not exceed eleven.

- 2. The number of exponent digits per channel must not exceed three.

- 3. If the direction of a transfer is different between channels A and B, channel B may have only function digits.

If any of these restrictions are violated, an error message will be generated. These error messages are listed in Section 3.

Note: The ports are always assigned in consecutive order starting with channel A mantissa (PO) exponent A, function A, mantissa B, exponent B and function B. If a field isn't needed, it will be ignored if it isn't specified.

Now consider port P10, a special port different from the others. If port P10 is selected by software to be a part of a channel, it may be used to represent mantissa, exponent or function digits for either channel. If port P10 isn't selected to be a part of either channel, it may be used as an output-only control port independent of both channels.

Port P11 contains the sign bits which have dedicated assignments and cannot be changed by software. The assignments are as follows:

- S1 Mantissa Sign, Channel A

- S2 Exponent Sign, Channel A

- S3 Mantissa Sign, Channel B

- S4 Exponent Sign, Channel B

# Preparing Cable Ends/Wire Color Codes

At this point in the installation procedure the interface cable should have already been cut to meet the needs of your installation. This discussion will assist you in preparing the ends of the interface cable. The cable ends should be prepared before the interface is installed in the computer.

Since there are numerous installation considerations and a variety of BCD peripherals available, there cannot be a universal method for preparing the cable ends for all peripherals. There are, however, a few general procedures you can follow.

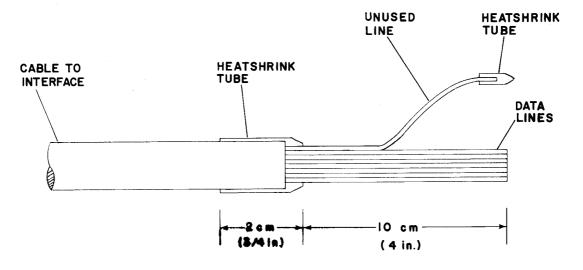

First, determine how much cable wires need to fan out from the main body of the cable(s) in order to connect your peripheral(s). This can vary considerably from one device to the next because of the spacing of the terminating locations on the peripheral. You should also keep in mind that you may be terminating one cable to two devices. Once you decide how much the cable wires need to fan out, refer to figure 2-7 and cut off the outer insulation of the cable to accommodate this. Then cut the shield off even with the outer insulation and place heat shrink tubing tape around the cable(s) so that none of the shield is exposed.

Figure 2-7. Cable Preparation

The color code for the cable wires is the same as the standard resistor color code. Digits have the following significance:

|             |        |               | 0 — Black  |

|-------------|--------|---------------|------------|

|             |        |               | 1 — Brown  |

| Most        |        |               | 2 — Red    |

| Prevalent → | XXX    | ← Narrow Band | 3 — Orange |

| Color       |        |               | 4 — Yellow |

|             | t      |               | 5 — Green  |

|             | Widest |               | 6 — Blue   |

|             | Band   |               | 7 — Violet |

|             |        |               | 8 — Grey   |

|             |        |               | 9 — White  |

If only one number is given for the color code, the wire will be a solid color (i.e., a "1" specifies a solid brown wire). If two numbers are given, the wire will have two colors (i.e., "94" specifies the most prevalent color is white and has a yellow band). Three numbers indicate the wire has three colors (i.e., "902" specifies the most prevalent color is white, the widest band is black and the narrow band is red).

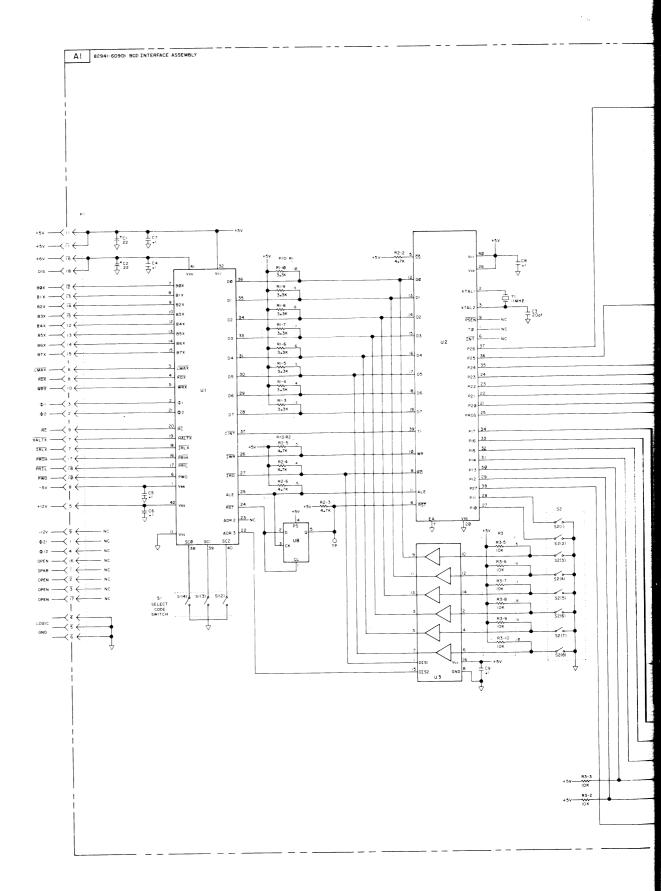

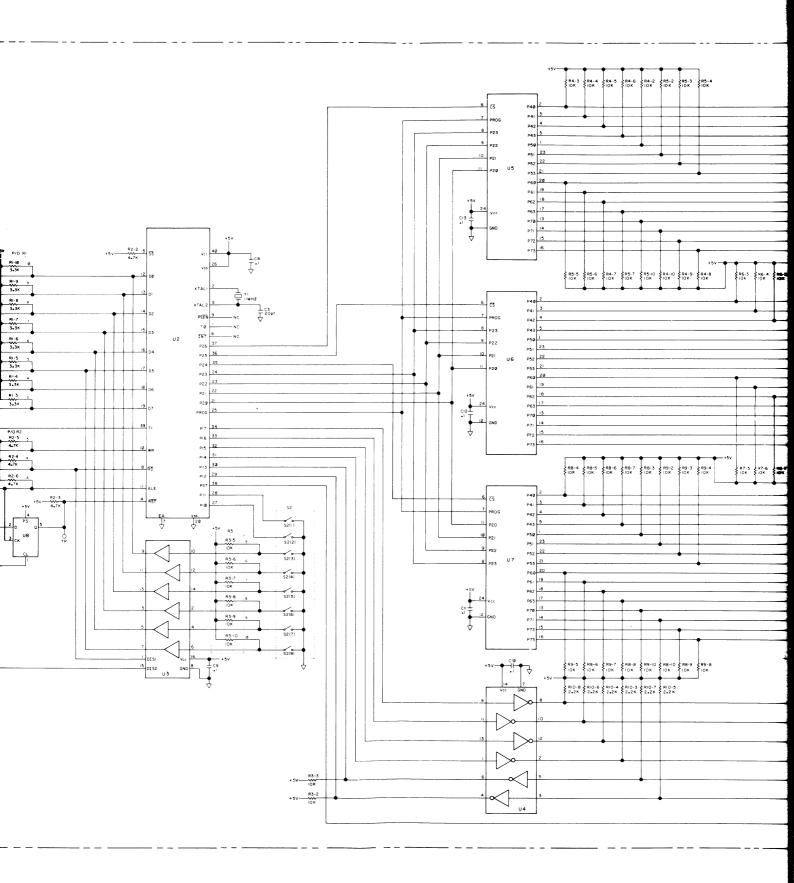

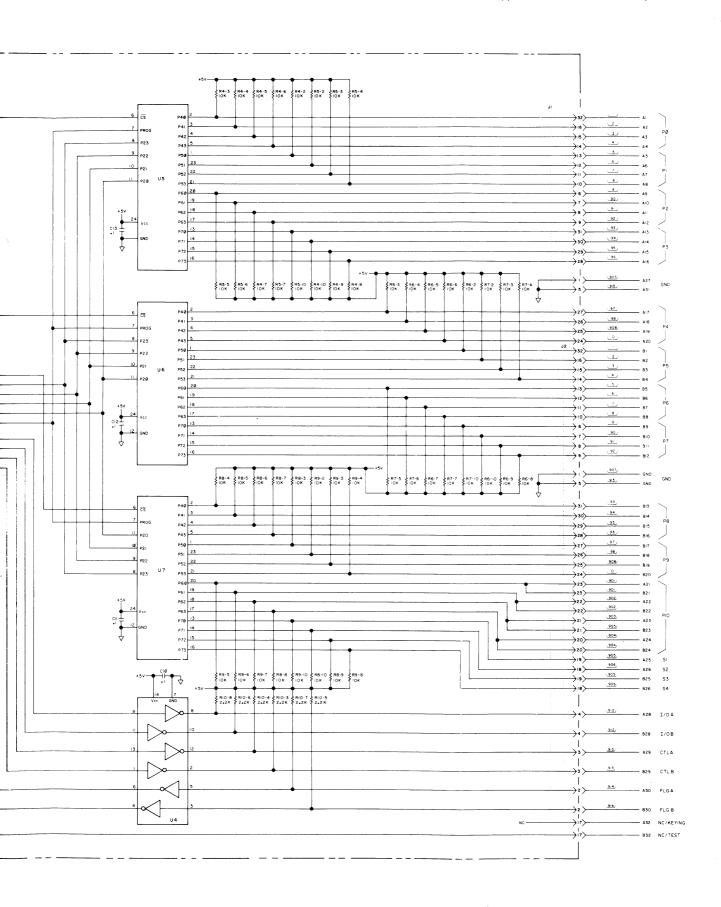

Refer to tables 2-3 and 2-4 and determine which BCD lines you intend to connect to your peripherals(s). It may also be helpful to fold out the schematics located in the back of this manual as you identify the cable wires needed for your installation. Remove only enough insulation from each wire you intend to use to accomplish your installation. Do not remove an excessive amount of insulation from the wires as they may short together or to other conductive surfaces. Some BCD peripherals may require that the cable wires be soldered to a circuit board. If this is the case, make sure not to remove so much insulation that the wires could protrude through the circuit board holes and short together or with other conductive surfaces.

After the insulation is removed from the cable wires you intend to use, proceed with installing the interface and connecting peripherals. Do not connect any of the cable wires to a peripheral without the interface installed in an HP Series 80 Personal Computer port.

Table 2-3. Cable A Wire Colors

Handshake Lines and Sign Bits

| Mnemonic                         | Wire Color |

|----------------------------------|------------|

| I/OA                             | 912        |

| CTLA                             | 913        |

| FLGA                             | 914        |

| S1 (Mantissa Sign, Channel A)    | 905        |

| S2 (Exponent Sign, Channel A)    | 906        |

| A and B GND                      | 907, 915   |

| A and B Shield (these should not | _          |

| be connected to the peripheral)  |            |

**Digit Ports**

| Significance | S | igi | nifi | ica | nc | e |

|--------------|---|-----|------|-----|----|---|

|--------------|---|-----|------|-----|----|---|

Wire Color Code

| Port | Standard Default Fomart      | Option Default Format        | MSB<br>(8) | (4) | (2) | LSB<br>(1) |

|------|------------------------------|------------------------------|------------|-----|-----|------------|

| PO   | Mantissa Digit 1 (Channel A) | Mantissa Digit 1 (Channel A) | 4          | 3   | 2   | 1          |

| P1   | Mantissa Digit 2 (Channel A) | Mantissa Digit 2 (Channel A) | 8          | 7   | 6   | 5          |

| P2   | Mantissa Digit 3 (Channel A) | Mantissa Digit 3 (Channel A) | 92         | 91  | 90  | 9          |

| P3   | Mantissa Digit 4 (Channel A) | Mantissa Digit 4 (Channel A) | 96         | 95  | 94  | 93         |

| P4   | Mantissa Digit 5 (Channel A) | Function Digit (Channel A)   | 0          | 908 | 98  | 97         |

| P10  | Special Control Port         | Special Control Port         | 904        | 903 | 902 | 901        |

Table 2-4. Cable B Wire Colors

# Handshake Lines and Sign Bits

| Mnemonic                         | Wire Color |

|----------------------------------|------------|

| I/OB                             | 912        |

| CTLB                             | 913        |

| FLGB                             | 914        |

| S3 (Mantissa Sign, Channel B)    | 905        |

| S4 (Exponent Sign, Channel B)    | 906        |

| A and B GND                      | 907, 915   |

| A and B Shield (these should not | _          |

| be connected to the peripheral)  |            |

**Digit Ports**

#### **Significance**

# Wire Color Code

| Port | Standard Default Format      | Option Default Format        | MSB<br>(8) | (4) | (2) | LSB<br>(1) |

|------|------------------------------|------------------------------|------------|-----|-----|------------|

| P5   | Mantissa Digit 6 (Channel A) | Mantissa Digit 1 (Channel B) | 4          | 3   | 2   | 1          |

| P6   | Mantissa Digit 7 (Channel A) | Mantissa Digit 2 (Channel B) | 8          | 7   | 6   | 5          |

| P7   | Mantissa Digit 8 (Channel A) | Mantissa Digit 3 (Channel B) | 92         | 91  | 90  | 9          |

| Р8   | Exponent Digit (Channel A)   | Mantissa Digit (Channel B)   | 96         | 95  | 94  | 93         |

| P9   | Function Digit (Channel A)   | Function Digit (Channel B)   | 0          | 908 | 98  | 97         |

| P10  | Special Control Port         | Special Control Port         | 904        | 903 | 902 | 901        |

# Handshake Line Mnemonic Variations

Before proceeding with installing the interface or connecting a peripheral, let's look at where the I/O, CTL and FLG lines should be terminated on a BCD device. There is no simple answer to this since BCD instruments made by different manufacturers (and often different instruments made by the same manufacturer) give various names to these lines.

Most BCD devices manufactured by Hewlett-Packard call the CTL line External Trigger and the FLG response line Print Command. Other common names for the CTL line are:

- Trigger

- External Encode

- Sample

The FLG response line might be called:

- Print

- Print Enable

- Ready

- Data Flag

Often, the only way to know where to terminate these lines on the BCD instrument is to read the description of the lines in the operating manual for that instrument. In section 3 a handshake sequence is given where the CTL, FLG and I/O lines are discussed in detail. In this discussion, a brief description is adequate.

The CTL line initiates a transfer when it is true. So, as you examine the description of the lines in the BCD instrument's operating manual, look for key words that mean the same thing. For example, the key words in the description might typically be something like *initiates a measurement*. The description of the line may also tell you which logic sense and handshake configuration (trailing or leading edge) you need.

The FLG response line is a ready/busy indicator from the peripheral. It goes true at the beginning of a reading and returns false when the reading is complete. The description for the FLG line would most likely reference something similar to this and it may also reference a print command like HIGH to LOW transition constitutes a print command.

The I/O line is used by the interface to tell the BCD peripheral whether the interface is specifying an input or an output. When it is true, an output is specified; when it is false, an input is specified. Therefore, if the BCD instrument can't do both, the I/O line will not be required. If the peripheral can receive and send data, look for something in the line description that references I/O operations.

# Installing the Interface and Connecting Peripherals

This procedure should be read and understood before you install the interface or connect a peripheral to it.

# **Safety Precautions**

Manufacturers of peripheral devices often use different grounding techniques. In some instances, logic ground is allowed to float with respect to earth ground in an effort to reduce ground return interference with digital signals. This may cause a voltage level between the two grounds to be high enough to be hazardous. Therefore, care should be taken when you are installing the interface or when peripherals are being connected to or disconnected from the interface.

On the BCD Interface, the ground contact connects to the cable shield, and, when the interface is installed on the computer, the ground contact connects to earth ground and to logic ground. On the peripheral end of the cable, the shield is not terminated to any ground. By not connecting the cable shield on the peripheral end, two things are accomplished:

- The possibility of ground loop problems are greatly reduced.

- If the peripheral's ground is floating or defective, touching the ground contact when the interface is removed from an I/O slot cannot result in a shock hazard.

You should keep in mind, however, if the interface is removed from an I/O slot while it is connected to a peripheral, logic ground does appear on the edge connector of the interface. Unless you know the voltage level of logic ground with reference to earth ground, never touch the edge connector while the interface is terminated to a peripheral.

#### WARNING

To avoid personal injury and equipment damage, read and understand the preceding safety precautions and do not deviate from the order of the following steps to install the interface and peripheral(s). Before proceeding, make sure the cable shield has been insualted with heat shrink tubing or electrical tape.

- 1. Turn the computer power switch to the OFF position. However, make sure the computer is plugged into a grounded (3-wire) ac outlet.

- 2. Remove the protective covers from two of the I/O ports to accommodate the interface and ROM Drawer. Any remaining unused I/O ports should be kept covered.

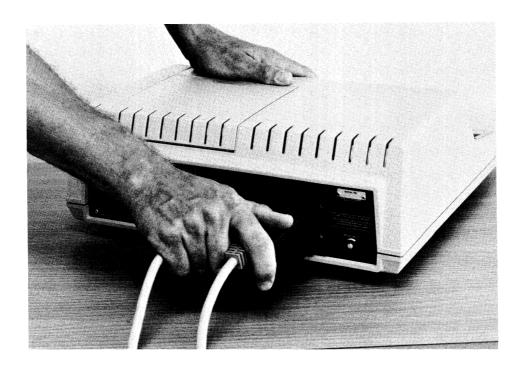

- 3. Refer to figure 2-8 to install the interface. Notice that the interface is keyed to prevent it from being inserted upside-down. In a like manner, install the ROM Drawer into an I/O port making sure that it contains the I/O ROM module.

Figure 2-8. Installing the Interface

- 4. Turn the power switch of all peripherals to be connected to the OFF position.

- 5. Refer back to tables 2-3 and 2-4 and connect the appropriate cable wires to your peripheral(s). If you are using a two-cable configuration, make sure to identify the A and B cables, as the same wire colors appear in both cables.

- 6. If there are unused wires after your periphrals are connected, you may use either of two options:

- Leave each wire unterminated, in which case the line will float high.

- Terminate each wire individually through a  $1k\Omega$  resistor to logic ground on the peripheral. This method is useful for a partially used port where unused bits must be tied low.

Let's consider each option individually.

In most instances, leaving unused lines floating is acceptable. If you choose to do this, each unused wire should be individually sleeved with heat shrink tubing to prevent them from coming in contact with each other or another conductive surface. The major factor determining whether or not you should use this option is the software used by your system. Keep in mind that if you leave a port floating high, it will be interpreted as a question mark or as a "0", depending upon which logic sense is configured (see table 1-1). Normally, however, an unused port would never be read or written to. If an unterminated port is inadvertently written to, it will have no adverse affect on the interface.

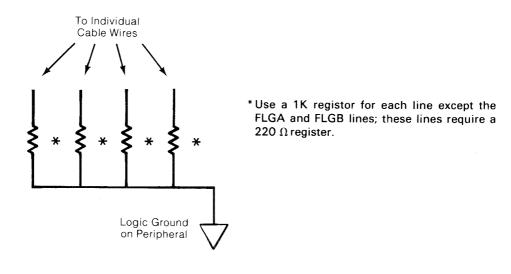

Terminating each wire individually through a separate resistor to the peripheral's logic ground is considerably more cumbersome. For example, if you have one port to terminate to logic ground, you will need four resistors, one for each wire. This is illustrated in figure 2-8. If you use this option, each wire terminated to logic ground, regardless of how many there are, must have a separate resistor. Never place any of the wires together and then connect them to the periphral's logic ground through a common resistor. Again, software is the major determining factor for using this option. If this option is used, care should be taken to never write to a port terminated to ground. This could cause equipment damage. It is also important that you properly insulate the side of each resistor connected to a wire to prevent a short from occuring.

Figure 2-9. Terminating Unused Lines to Logic Ground

7. Turn the power switches of the computer and peripheral(s) to the ON position.

# Removing Peripherals/Disconnecting the Interface

Use the following steps in the order given to disconnect peripherals from the interface or to disconnect the interface from the computer.

#### **CAUTION**

Do not remove the interface from an I/O port with the computer power switch on. Doing this will cause damage to either the interface, the computer or both.

- 1. Turn all peripheral power switches off.

- 2. Turn the computer power switch off.

- 3. Remove the interface cable wires from the peripheral(s) you are disconnecting from the interface. If there are two peripherals and only one is to be disconnected, each wire removed must be individually sleeved or terminated to the peripheral's logic ground before power is returned to the computer. This was explained in step 6 of the installation procedure. If you intend to remove the interface from the I/O slot, proceed with step 4.

- 4. If the interface is removed from the I/O port while it is terminated to a peripheral, care should be taken not to touch the edge connector of the interface. Logic ground of the peripheral appears on this connector. If this ground is floating or defective, touching the edge connector may expose you to an electrical shock hazard.

# Using Your BCD Interface

## Introduction

The HP 82941A BCD Interface enables your HP Series 80 Personal Computer to communicate with a variety of instruments that present data in Binary Coded Decimal (BCD) format. This section explains how to program the interface.

# **Binary Coded Decimal**

Binary Coded Decimal is, as the name implies, a method of encoding the decimal digits (0 through 9) in a four bit binary format. The following table shows the binary coding of the ten decimal digits and six additional ASCII characters that are allowed. The interface can be programmed through default switches or program statements to recognize either positive-true or negative-true logic. The table shows the allowable ASCII characters and the associated BCD codes for each logic sense.

**ASCII Positive True Negative True** < = >

Table 3-1. BCD Coding

#### **Data and Handshake Lines**

Data and handshake lines are provided as follows:

- Data 44 bi-directional data lines organized as 11 four-bit ports (P0 through P10).

- Sign Bits four sign bits (S1 through S4) through port P11.

- Handshake four output handshake lines (I/OA, I/OB, CTLA, CTLB).

# **Operating Modes**

The operating mode refers to selecting the fields as shown in the next table.

Table 3-2. Operating Mode

| Field                                              | Range                                                   |

|----------------------------------------------------|---------------------------------------------------------|

| Number of channels                                 | A, B, or both.                                          |

| Channel Direction                                  | Input or output.                                        |

| Number of mantissa digits in each channel*         | 0 through 11.                                           |

| Number of exponent digits for each channel*        | 0 through 3.                                            |

| Number of function digits in each channel*         | 0 through 11.                                           |

| Decimal point placement for each mantissa          | May be placed before any mantissa digit.                |

| Logic sense of all signals<br>Handshake triggering | Positive or negative true.<br>Leading or trailing edge. |

# **Default Formats**

The BCD interface provides two standard default formats: single and dual channel. These formats are selected by changing the reset switch (S2) switch 1 or by program control. The default formats and their associated port assignments are shown in the next tables.

Table 3-3. Single Channel Format (S2 switch 1 = "0" position)

| Number of Ports | Ports (or bits) Used | Data      | Handshake |

|-----------------|----------------------|-----------|-----------|

| 8               | PO through P7        | Mantissa  | Channel A |

| 1               | P8                   | Exponent  | Channel A |

| 1               | P9                   | Function  | Channel A |

| 1/2             | P11 (bits S1 and S2) | Sign Bits | Channel A |

Table 3-4. Dual Channel Format (S2 switch 1 = "1" position)

| Number of Ports | Ports (or bits) Used | Data      | Handshake |

|-----------------|----------------------|-----------|-----------|

| 4               | PO through P3        | Mantissa  | Channel A |

| 1               | P4                   | Function  | Channel A |

| 4               | P5 through P8        | Mantissa  | Channel B |

| 1               | P9                   | Function  | Channel B |

| 1/2             | P11 (bits S1 and S2) | Sign Bits | Channel A |

| 1/2             | P11 (bits S3 and S4) | Sign Bits | Channel B |

Examples are provided following the discussion of the interface registers to show how to select these and other formats with program statements.

f \* The combined sum of mantissa, function, and exponent digits specified cannot exceed 11.

#### **Data Rates**

The data transfer rate depends upon the direction of the transfer, the type of transfer (normal, fast handshake, or interrupt), concurrent operations taking place and peripheral timing. The maximum data rates that the interface can handle are as follows:

Table 3-5. Transfer Rates

| Transfer Type  | Input           | Output          |  |  |

|----------------|-----------------|-----------------|--|--|

| Fast Handshake | 20k bytes/sec   | 22 bytes/sec    |  |  |

| Normal ENTER   | 7.75k bytes/sec | 4.75k bytes/sec |  |  |

| Interrupt      | 400 bytes/sec   | 400 bytes/sec   |  |  |

The data rates shown for the fast handshake mode are achieved by placing the following restrictions on the fast handshake mode:

- 1. Standard Format

- Channel A only (one peripheral).

- Eight mantissa digits only.

- One exponent digit only.

- Function digit may be selected but is ignored.

- Mantissa and exponent signs will be transferred.

- 2. Byte count must be specified on an input.

- 3. Positive true logic on data lines.

- 4. Trailing edge handshake only.

- 5. Decimal points may be selected but will not be transferred.

- 6. ASCII codes 0 through 32 and 44 (comma) cannot be used for output.

If the peripheral fails to complete a handshake during the fast handshake mode, the CPU in the computer halts and the system hangs up. To recover, the FLGB line, unused in the fast handshake mode format, may be used to indicate errors by the peripheral. If FLGB goes true while the interface is waiting for a handshake, the fast handshake mode is terminated and Error 115 is displayed.

#### **Program Statements**

The following program statements are implemented by the BCD interface card. See the syntax reference in the I/O ROM Owner's Manual for a complete description of these statements.

| ABORTIO* |  |

|----------|--|

| HSSERT*  |  |

| HALT*    |  |

| CONTROL  |  |

ENABLE INTR ENTER OUTPUT REMOTE RESET SEND CMD SEND DATA SEND TALK SEND LISTEN STATUS\* TRANSFER

# Using the Interface

This discussion assumes that you have read the I/O ROM Owner's Manual.

# **Programming With Default Formats**

This discussion shows how to program the interface with the single or dual channel default formats that are provided. Factory settings are assumed for the interface select code and the default switches. The factory settings are:

- Interface Select Code (S1) = 3 (all set to the "0" position).

- Reset Default Switches (S2) = all set to the "0" position.

#### Example 1

Run the following program:

```

10 RESET 3 ! RESET INTERFACE

3,0 ; R0,R1,R2,C3,C4,C5,C6,C7,C8,C9,C0

20 STATUS

30 IMAGE K, X, DD, /

! PRINT FORMAT

"READ REG 0=";R0,"READ REG 1=";R1

40 PRINT

USING

30

"READ REG 2=";R2

50 PRINT

USING

30

"REG 3=";C3,"REG 4=";C4,"REG 5=";C5

30

60 PRINT USING

"REG 6=")C6,"REG 7=")C7,"REG 8=")C8

70 PRINT USING 30

"REG 9=":C9."REG 10=":C0

80 PRINT USING 30 ;

90 END

```

#### Here is the printout:

```

READ REG 0=

....

-Interface I.D.

-Interrupt Mask

READ REG

1 ==

Ø

READ REG

2=

-Handshake Lines

-Mantissa Digits Specified

REG 3=

REG

4=

1

-Exponent Digits Specified

5=

REG

-Function Digits Specified

1

REG

6=

0

—Decimal Point Location

REG

Ø

-Handshake Logic Sense

REG

0

-Data Logic Sense

REG 9=

-Function Logic Sense

10=

REG

-Signs and Port 10 Logic Sense

```

Note that Read Register 0 and Registers 3, 4, and 5 are not zero. Read Register 0 identifies the interface as the BCD interface. Register 3 indicates the number of mantissa digits to be input (in this case eight). Register 4 indicates the number of exponent digits (one) to be input and Register 5 indicates the number of function digits (one) to be input. Registers 7 through 10 indicate the logic sense of the various data and handshake lines (the value of 0 indicates positive true logic sense). Read registers 1 and 2 and Register 6 are not used for this example and are discussed later in this section.

<sup>\*</sup> Executing this statement interrupts any I/O operation that may be in progress.

Assume that you are connected to a digital multimeter. The multimeter outputs eight significant data digits, a one-digit exponent, and a one-digit function value. All logic senses (data, handshake, etc.) are defined as positive true.

The following program reads the data from the multimeter and prints the results:

```

10 RESET 3 ! RESET INTERFACE

20 ENTER 3 ; D1,F1 ! GET CHANNEL A DATA

30 PRINT "READING=";D1

40 PRINT "FUNCTION=";F1

50 STOP

```

#### Here is a typical printout:

```

READING= 1250.524

FUNCTION= 1

```

#### Example 3

The function value is used to indicate the position of the function switch (ohms, volts, amps, etc.) located on the multimeter. Let the function values be defined as:

```

1 = Ohms

2 = Volts AC

3 = Amps

4 = Volts DC

```

#### Run the following program:

```

10 RESET 3 ! RESET INTERFACE

20 ENTER 3 ; D1,F1 ! GET CHANNEL A DATA

30 ON F1 GOSUB 70,90,110,130 ! CHANNEL A BRANCHES

40 PRINT "READING=";D1;Z*

50 PRINT "FUNCTION=";F1

60 STOP

70 Z$="OHMS" ! FUNCTION =1

80 RETURN

90 Z$="VOLTS-AC" ! FUNCTION =2

100 RETURN

110 Z$="AMPS" ! FUNCTION =3

120 RETURN

130 Z$="VOLTS-DC" ! FUNCTION =4

140 RETURN

```

## Here are typical results:

```

READING= 1250.524 OHMS

FUNCTION= 1

```

The BCD interface can be connected to two BCD devices simultaneously. Set the reset default switch (S2, switch 1) to the "1" position. This changes the default mode of the interface to two channel operation. Run the following program:

```

10 RESET 3 ! RESET

INTERFACE

STATUS 3,0

20

;/R0,R1,R2,C3,C4,C5,C6,C7,C8,C9,C0

30

PRINT FORMAT

IMAGE K.X.DD./

USING 30 ;

"READ REG 0=":R0."READ REG 1=":R1

"READ REG 2=":R2

50 PRINT USING

30

"REG 3=";C3,"REG

4=";C4,"REG 5=";C5

60 PRINT

USING

30

"REG 6=";C6,"REG 7=";C7,"REG 8=";C8

"REG 9=';C9,"REG 10=";C0

30 ;

70 PRINT USING

80 PRINT USING 30 ;

90 END

```

#### Here are the results:

| READ REG 0= | 3 | —Interface I.D.                |

|-------------|---|--------------------------------|

| READ REG 1= | Ø | —Interrupt Mask                |

| READ REG 2= | Ø | —Handshake Lines               |

| REG 3= 68   |   | -Mantissa Digits Specified     |

| REG 4= 0    |   | -Exponent Digits Specified     |

| REG 5= 17   |   | -Function Digits Specified     |

| REG 6= 0    |   | —Decimal Point Location        |

| REG 7= 0    |   | —Handshake Logic Sense         |

| REG 8= 0    |   | -Data Logic Sense              |

| REG 9= 0    |   | -Function Logic Sense          |

| REG 10= 0   |   | -Signs and Port 10 Logic Sense |

Note that registers 3, 4, and 5 values are different than those obtained for example 1.

The value (68) for Register 3 indicates that four mantissa digits are reserved for channel A input and four mantissa digits are reserved for channel B input. The value (0) for Register 4 indicates that neither channel is using an exponent digit. The value (17) for Register 5 indicates that each channel has one digit reserved for input function data.

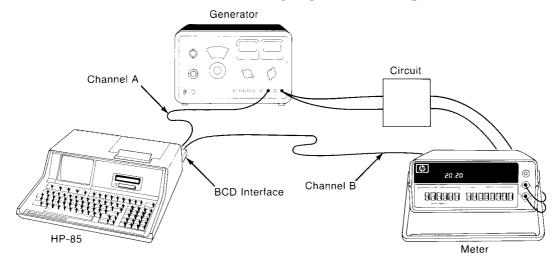

For example, the interface might be connected to a signal generator and a digital voltmeter:

Figure 3-1. Typical Test System Connection

The signal generator is driving a circuit under test for frequency response. The voltmeter takes readings of the circuit output. By comparing the voltage vs. frequency readings, the bandpass of the circuit is determined.

Here is an example program. Typical frequency and voltage parameters are used.

```

10 ENTER 3 ; A1,F1,B2,F2 ! GET CHANNEL A AND

B DATA

20 DISP A1;F1;B2;F2 ! DISPLAY DATA

30 ON F1 GOSUB 80,120,160 ! CHANNEL A

FUNCTION BRANCHES

40 ON F2 GOSUB 100,140,180 ! CHANNEL B

FUNCTION BRANCHES

50 PRINT A1:2$

60 PRINT B2;Y$

70 STOP

80 Z$="Hz" ! A FUNCTION =1

90 RETURN

100 Y$="Microvolts" ! B FUNCTION =1

110 RETURN

Z#="KHz" ! A FUNCTION =2

120

130 RETURN

140 Y$="Millivolts" ! B FUNCTION =2

150 RETURN

160 Z = "MHz" ! A FUNCTION = 3

170 RETURN

180 \text{ Y} = \text{"Volts"} + \text{B FUNCTION} = 3

190 RETURN

```

Run the program. Here is a typical result:

```

1000 Hz

2020 Microvolts

```

# **Partial Fields**

The examples shown thus far enter the input data from the interface in the following order: mantissa A, function A, mantissa B, function B. You cannot enter a portion (or field) of data (e.g., mantissa B) without first entering all preceding data. Partial field addressing is provided to enable you to access only the data that you desire. Partial field addressing is accomplished by specifying primary addresses 00 through 06. The partial field specifiers and the data that they access are shown in the next table. Interface select code 3 is assumed.

| lable 3-6. | Partial | Field | Specification |

|------------|---------|-------|---------------|

|------------|---------|-------|---------------|

| Device<br>Selector | Data Entered                                |

|--------------------|---------------------------------------------|

| 300                | All data (Default)                          |

| 301                | Channel A mantissa, exponent, and function. |

| 302                | Channel B mantissa, exponent, and function. |

| 303                | Channel A mantissa and exponent.            |

| 304                | Channel B mantissa and exponent.            |

| 305                | Channel A function.                         |

| 306                | Channel B function.                         |

Run the previous program (example 5) and observe the results. Execute the following statements and observe the results shown here.

|                | 300;A1,F1,B2,F2<br>A1;F1;B2;F2 | 1000 | 1 | 2020 | 1 |

|----------------|--------------------------------|------|---|------|---|

| ENTER<br>PRINT | 301;A1,F1<br>A1;F1             | 1000 | 1 |      |   |

|                | 302;B2,F2<br>B2;F2             | 2020 | 1 |      |   |

| ENTER<br>PRINT | 303;A1<br>A1                   | 1000 |   |      |   |

| ENTER<br>PRINT | 304;B2<br>B2                   | 2020 |   |      |   |

| ENTER<br>PRINT | 305;F1<br>F1                   | 1    |   |      |   |

| ENTER<br>PRINT | 306;F2<br>F2                   | 1    |   |      |   |

Once a partial field has been specified, that field remains in effect until a new field is selected or the interface is reset.

The REMOTE statement can also be used to set a partial field specifier provided the address ranges from 00 to 06. Thus the sequence—

```

REMOTE 306

ENTER 3; F2

PRINT F2

```

could also be used to enter and print the channel B function data. This would be especially useful when documenting or debugging a program since the REMOTE statements stand out amongst the EMTER and OUTPUT statements.

Partial fields are addressed by ENTER, OUTPUT, SEND TALK, SEND LISTEN and SEND CMD statements.

#### Port 10

The previous examples show how to take readings from external devices. The operator is required to manually set the instrument functions (frequency, function, etc.). The BCD interface provides a special port to allow control of external instruments from the program. This discussion explains how to use port 10 for output.

In the two channel example (example 5), the BCD interface ports are dedicated as follows:

- Ports P0 through P3 Signal generator frequency reading.

- Port P4 Signal generator function (range switch).

- Ports P5 through P8 Voltmeter reading.

- Port P9 Voltmeter function (voltage range switch).

- Port 10 Unused.

Port 10 is a special purpose port that can be used as an input or output port. Port 10 is the only port that can be used as an output port without setting the reset default switch S2(8) to the output enable position. Port 10 is accessed by performing a control operation to the four least significant bits of Write Register 2. For example: CONTROL 3, 2:15 sets all four bits of port 10. The next example assumes the same instrument configuration and function values as those used for example 5.

The function values returned are the same as defined for that example.

The following assumptions about the signal generator are made:

- The generator sweep values range from 1 through 1000.

- A bit can be set to begin the sweep at 1.

- The generator has three ranges.

- Each range can be externally selected.

Here is the bit mask for the generator:

| Bit 3               | Bit 2               | Bit 1              | Bit 0                 |

|---------------------|---------------------|--------------------|-----------------------|

| 1 =<br>MHz<br>Range | 1 =<br>KHz<br>Range | 1 =<br>Hz<br>Range | 1 =<br>Start<br>Sweep |

| Value = 8           | Value = 4           | Value = 2          | Value = 1             |

#### Example 7

The program initially sets the generator to the 1 Hz range and starts the sweep. When the sweep reaches 1000 Hz, the program switches the generator to the KHz range and restarts the sweep. When the sweep reaches 1000 KHz, the program switches the generator to the MHz range and again restarts the sweep. When the sweep reaches 1000 MHz, the entire program is restarted. Here is the program:

```

10 CONTROL 3,2; 3! SET PORT 10 OUTPUT VALUE

TO 3

20 ENTER 3 ; A1,F1,B2,F2 ! ENTER CHANNEL A

AND B DATA

30 IF A>999 THEN GOTO 230 ! CHECK TO CHANGE

FREQ

40 DISP A1;F1;B2;F2

50 ON F1 GOSUB 110,150,190 ! CHANNEL A

FUNCTION BRANCHES

60 ON F2 GOSUB 130,170,210 ! CHANNEL B

FUNCTION BRANCHES

70 DISP A1;Z#

80 DISP B2;Y$

90 GOTO 20

100 END

110 Z#="Hz" ! A FUNCTION =1

120 RETURN

130 Y$="Microvolts" ! B FUNCTION =1

140 RETURN

150 Z$="KHz" ! A FUNCTION =2

160 RETURN

170 Y$="Millivolts" ! B FUNCTION =2

180 RETURN

Z = "MHz" ! A FUNCTION = 3

190

200 RETURN

210 Y = "Volts" ! B FUNCTION = 3

220 RETURN

230 IF F1K3 THEN 250 ! CHECK FOR MAX FREQ RANGE

240 GOTO 10

250 CONTROL 3,2 ; 2^(F1+1)+1 ! CHANGE GENERATOR FUNCTION

260 GOTO 20

```

#### Interrupts

The BCD interface provides program interrupt. Interrupts are generated only from the most-significant digit of the function. If you are only inputting one digit of function information (see the previous example), then this digit generates the interrupt. You enable the interrupt mask to Write Register 1 with an ENRELE INTE and specify a BASIC service routine with an ON INTE statement.

#### Example 8

Let's change the previous example to generate an interrupt if the voltmeter detects an overrange condition. Assume that the voltmeter returns a function value of 8 when an overrange is detected. Add the following program lines to the program used for the previous example:

```

1 ON INTR 3 GOSUB 300

2 ENABLE INTR 3;128 ! INTERRUPT FOR BIT 3 OF FUNCTION B

```

## **Existing Program**

```

300 STATUS 3,1 ; S1

310 IF S1<128 THEN ENABLE INTR 3;128 @ RETURN ! INT.CAUSE

320 DISP "METER OVERRANGE"

330 STOP

```

Line 1 - defines the program branch.

Line 2 - defines the bit in the function digit that can cause an interrupt (see Write Register 1) and enables the interrupt.

Line 300 - enters the value of read register 1 into variable S1. The status of Read Register 1 must ALWAYS be checked following an interrupt. Subsequent interrupts are prevented until this interrupt is serviced.

Line 310 - checks to see which bit of the function digit caused the interrupt. This check is used to prioritize the interrupts when more than one bit generates the interrupt (see multiple interrupts). This line also re-enables the interrupt with a new control word (128) to Write Register 1 if the function A value returned is less than 128 (bit 7 not set). Notice that the EETUEN statement is placed on the same line as the ENABLE INTE statement.

## Multiple Interrupts

More than 1 bit of the function value can be specified to generate an interrupt. This feature allows you to define the priorities of the interrupts. Here is an example routine to service multiple interrupts. Note that the bit 3 routine is serviced prior to the bit 0 routine if they both occur.

#### Example 9

```

10 ON INTR 3 GOSUB 200

20 ENABLE INTR 3;9 ! INTERRUPT BITS

```

# Main Program

```

200 STATUS 3,1; S1

210 IF BIT(S1,3) THEN 240

220 PRINT "BIT 0 DETECTED"

230 ENABLE INTR 3:9 @ RETURN

240 PRINT "BIT 3 DETECTED"

250 IF BIT(S1,0) THEN 220

260 ENABLE INTR 3:9 @ RETURN

```

Line 20 - specifies bits 0 and 3 to generate an interrupt.

Line 200 - enters the status byte from Read Register 1 (interrupt cause).

Line 210 - checks for a bit 3 interrupt (first priority). If bit 3 is true (set), the program branches to the bit 3 service routine (lines 240 through 260).

Line 220 - is the bit 0 service routine.

Line 230 - re-enables the interrupt and returns to the main program.

Line 240 - is the bit 3 service routine.

Line 250 - checks for a bit 0 interrupt (second priority). A program branch to the bit 0 routine (line 220) occurs only if bit 0 is true (set).

Line 260 - re-enables the interrupt and returns to the main program.

You determine the priorities for the interrupts. The bit 0 interrupt can be defined as having the higher priority by exchanging the arguments of the bit functions (lines 210 and 250).

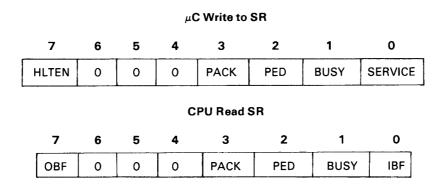

# Registers

The interface contains 13 registers that can be accessed from the HP Series 80 Personal Computers. These registers are divided into three groups: read registers, write registers, and bi-directional registers. Read registers are accessed with the STATUS statement. Write registers are accessed with the CONTROL statement. The bi-directional registers are accessed with either the STATUS (input) statement or the CONTROL (output) statement. Other statements (ASSERT, ENABLE INTR) access specific registers only and are explained with the register description. This discussion explains each register and shows the access procedure.

Note: The default values shown for all registers assume that the reset default switch (S2) is set to the factory setting (all "0"s). Positive-true logic sense is assumed for all descriptions.

# Read Register 0

#### Interface ID

| Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Always<br>0 | Always<br>0 | Always<br>0 | Always<br>0 | Always<br>0 | Always<br>0 | Always<br>1 | Always<br>1 |

| Value = 128 | Value = 64  | Value = 32  | Value = 16  | Value = 8   | Value = 4   | Value = 2   | Value = 1   |

To access this register execute:

STATUS 3,0;S0

The value returned (preset to 3) from this register is entered into variable S0. The value 3 indicates that this is the BCD interface.

## Read Register 1

# Interrupt Cause

| Bit 7                                              | Bit 6                                              | Bit 5 | Bit 4 | Bit 3                                                 | Bit 2     | Bit 1     | Bit O     |

|----------------------------------------------------|----------------------------------------------------|-------|-------|-------------------------------------------------------|-----------|-----------|-----------|

| Fu                                                 | Generated from Function B (Most Significant Digit) |       |       | Generated from<br>Function A (Most Significant Digit) |           |           |           |

| Value = 128   Value = 64   Value = 32   Value = 16 |                                                    |       |       | Value = 8                                             | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

```

STATUS 3,1;81

```

The value returned indicates the bit (or bits) that generated the interrupt. See Write Register 1 for a complete discussion about the BCD card interrupts.

Default value: 0

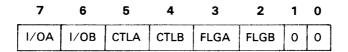

## Read Register 2

#### **Control Line Messages**

| Bit 7                      | Bit 6                            | Bit 5                            | Bit 4                            | Bit 3                     | Bit 2                           | Bit 1     | Bit O     |

|----------------------------|----------------------------------|----------------------------------|----------------------------------|---------------------------|---------------------------------|-----------|-----------|

| I/O A 0 = Input 1 = Output | I/O B<br>O = Input<br>1 = Output | Cntrl A<br>0 = Ready<br>1 = Busy | Cntrl B<br>0 = Ready<br>1 = Busy | Flag A 0 = Ready 1 = Busy | Flag B<br>0 = Ready<br>1 = Busy | 0         | 0         |

| Value = 128                | Value = 64                       | Value = 32                       | Value = 16                       | Value = 8                 | Value = 4                       | Value = 2 | Value = 1 |

STATUS 3,2;82

The value returned indicates the status of the various handshake signals.

# Default value: 0

The meanings of the various bits are described next.

- Bit 7 set (1) indicates that channel A ports are enabled for output operation. Bit 7 reset (0) indicates that channel A ports are set to the input mode.

- Bit 6 set (1) indicates that channel B ports are enabled for output operation. Bit 6 reset (0) indicates that channel B ports are set to the input mode.

- Bit 5 set (1) indicates that the channel A "Control" handshake line is active (busy). Bit 5 reset (0) indicates that the channel A "Control" handshake line is ready.

- Bit 4 set (1) indicates that the channel B "Control" handshake line is active (busy). Bit 4 reset (0) indicates that the channel B "Control" handshake line is ready.

- Bit 3 set (1) indicates that the channel A "Flag" handshake line is busy. The peripheral device connected to channel A uses the "Flag" line to indicate its status to the computer. Bit 3 reset (0) indicates that the channel A peripheral is ready.

- Bit 2 set (1) indicates that the channel B "Flag" handshake line is busy. The peripheral device connected to channel B uses the "Flag" line to indicate its status to the computer. Bit 2 reset (0) indicates that the channel B peripheral is ready.

- Bits 1 and 0 are not used.

# Write Register 0

Write Register 0 is not implemented. Attempting to access Write Register 0 generates error 111.

# Write Register 1

#### Interrupt Mask

| Bit 7                                  | Bit 6      | Bit 5      | Bit 4                                  | Bit 3     | Bit 2     | Bit 1     | Bit O     |

|----------------------------------------|------------|------------|----------------------------------------|-----------|-----------|-----------|-----------|

| Function B<br>(Most Significant Digit) |            |            | Function A<br>(Most Significant Digit) |           |           |           |           |

| Value = 128                            | Value = 64 | Value = 32 | Value = 16                             | Value = 8 | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

ENABLE INTR 3; <mask value>

CONTROL 3, 1; <mask value>

Write Register 1 contains the interrupt mask for channel A and channel B. The interrupts are generated from the most significant digit of the function value of each channel. For example, assume that channel A is configured for two digit function values from an external device. These values range from 00 through 99. You can specify an interrupt only for values of the tens digit. The units digit cannot generate an interrupt. If a single digit function value is specified (default) then that single digit is the most significant digit and can generate an interrupt (see example 8).

# Write Register 2

## Handshake Lines and Port 10

| Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3                              | Bit 2     | Bit 1     | Bit 0     |

|---------------------|---------------------|---------------------|---------------------|------------------------------------|-----------|-----------|-----------|

| I/O<br>Channel<br>A | I/O<br>Channel<br>B | CTL<br>Channel<br>A | CTL<br>Channel<br>B | Port 10 Output<br>(when available) |           |           |           |

| Value = 128         | Value = 64          | Value = 32          | Value = 16          | Value = 8                          | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

CONTROL 3,2; <value>

ASSERT 3; <value>

Write Register 2 enables you to control the interface handshake lines from a program. The output data for port 10 (if port 10 is available for output) is also written to this register.

The meanings of the various bits are described next.

- Bit 7 set (1) enables channel A ports for output. The reset default switch (S2) switch 8 must be set to the "1" position. Attempting to set bit 7 with S2 switch 8 in the "0" position (default) generates error 113. Bit 7 clear (0) enables channel A ports for input.

- Bit 6 set (1) enables channel B ports for output. The reset default switch (S2) switch 8 must be set to the "1" position. Attempting to set bit 6 with S2 switch 8 in the "0" position (default) generates error 113. Bit 6 clear (0) enables channel B ports for input.

- Bit 5 enables you to control the CTL handshake line for channel A. This line remains active until the interface is reset or bit 5 is cleared (set to 0). If this bit is not reset, subsequent EMTER or CUTPUT operations generate error 118.

- Bit 4 enables you to control the CTL handshake line for channel B. This line remains active until the interface is reset or bit 4 is cleared (set to 0). If this bit is not reset, subsequent ENTER or QUITPUT operations generate error 118.

- Bits 3 through 0 are port 10. When port 10 is used as an output port, the data is written to these four bits (see example 7). The input/output switch (S2) switch 8 does not affect port 10. When port 10 is enabled as an input port or configured as part of a channel, any attempt to output to port 10 generates error 114.

## Register 3

#### **Mantissa Digits**

| Bit 7       | Bit 6                                                     | Bit 5 | Bit 3 | Bit 2     | Bit 1     | Bit O     |           |

|-------------|-----------------------------------------------------------|-------|-------|-----------|-----------|-----------|-----------|

|             | Number of Digits Assigned for Channel A Mantissa (0 — 11) |       |       |           |           |           |           |

| Value = 128 |                                                           |       |       | Value = 8 | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

```

STATUS 3,3;83

CONTROL 3,3;

```

The value contained in this register indicates how many mantissa digits are specified for each channel. To change this specification, execute the appropriate CONTROL statement to this register. The new specification remains in this register until changed by another CONTROL statement or until the interface is reset.

Reset default: 8 (Channel A only)

**Note:** The reset default value for two channel operation is 68. This indicates that four mantissa digits are specified for each channel (see example 4).

## Register 4

### **Exponent Digits**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 7       | Bit 6 | Bit 3                                 | Bit 2     | Bit 1     | Bit O     |           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|---------------------------------------|-----------|-----------|-----------|-----------|

| ACCIDING THE PROPERTY OF THE P |             |       | Number of<br>Assigned for<br>Exponent | Channel A |           |           |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Value = 128 |       |                                       | Value = 8 | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

The value contained in this register indicates how many exponent digits are specified for each channel. To change this specification, execute the appropriate CONTROL statement to this register. The new specification remains in this register until changed by another CONTROL statement or until the interface is reset.

Reset default: 1 (Channel A only)

**Note**: The reset default value for two channel operation is 0. This indicates that no exponent digits are specified for either channel.

## Register 5

## **Function Digits**

| Bit 7       | Bit 6      | Bit 3                           | Bit 2      | Bit 1     | Bit O     |           |           |

|-------------|------------|---------------------------------|------------|-----------|-----------|-----------|-----------|

|             |            | Number of Assigned for Function | Channel A  |           |           |           |           |

| Value = 128 | Value = 64 | Value = 32                      | Value = 16 | Value = 8 | Value = 4 | Value = 2 | Value = 1 |

To access this register execute:

The value contained in this register indicates how many function digits ar specified for each channel. To change this specification, execute the appropriate CONTROL statement to this register. The new specification remains in this register until changed by another CONTROL statement or until the interface is reset.

Reset default: 1 (Channel A only)

Note: The reset default value for two channel operation is 17. This indicates that one function digit is specified for each channel.

## Register 6

#### **Decimal Point Placement**

| Bit 7       | Bit 6                                                                                      | Bit 5 | Bit 3 | Bit 2 | Bit 1     | Bit 0                                              |           |

|-------------|--------------------------------------------------------------------------------------------|-------|-------|-------|-----------|----------------------------------------------------|-----------|

|             | Number of Mantissa<br>Digits Assigned to the<br>Right of the Decimal Point.<br>(Channel B) |       |       |       |           | Mantissa<br>gned to the<br>ecimal Point.<br>nel A) |           |

| Value = 128 | Value = 128                                                                                |       |       |       | Value = 4 | Value = 2                                          | Value = 1 |

To access this register execute:

STATUS 3,6;S6 CONTROL 3,6;<value>

The value contained in this register indicates how many mantissa digits to the right of the decimal point are specified. To change this specification, execute the appropriate CONTROL statement to this register. The new specification remains in this register until changed by another CONTROL statement or until the interface is reset. Note that the specification cannot exceed the number of mantissa digits specified for that channel. For example, if eight mantissa digits are specified for channel A, then a maximum of eight digits can be specified to the right of the decimal point for this channel. Decimal point placement can only be specified for input operations.

Reset default: 0

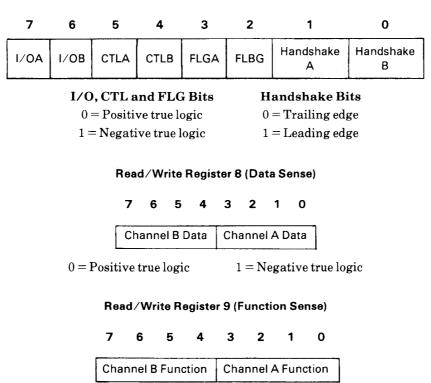

## Register 7

## Control Sense and Handshake Mode

| Bit 7                   | Bit 6                   | Bit 5                   | Bit 4                   | Bit 3                    | Bit 2                    | Bit 1                  | Bit 0                  |

|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|------------------------|------------------------|

| Logic<br>Sense<br>I/O A | Logic<br>Sense<br>I/O B | Logic<br>Sense<br>CTL A | Logic<br>Sense<br>CTL B | Logic<br>Sense<br>Flag A | Logic<br>Sense<br>Flag B | Handshake<br>Mode<br>A | Handshake<br>Mode<br>B |

| Value = 128             | Value = 64              | Value = 32              | Value = 16              | Value = 8                | Value = 4                | Value = 2              | Value = 1              |

#### To access this register execute:

```

STATUS 3,7;S7

CONTROL 3,7;

```

The value contained in this register indicates the logic sense of the control and handshake lines. To change this specification, execute the appropriate CONTROL statement to this register. The new specification remains in this register until changed by another CONTROL statement or until the interface is reset.

#### Reset default: 0

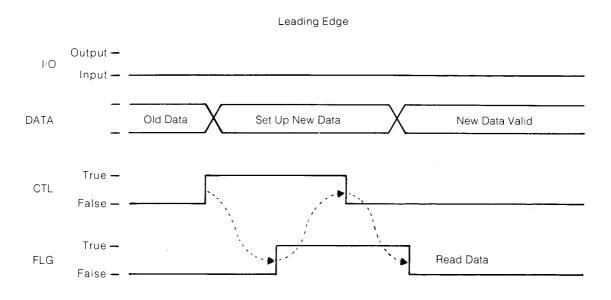

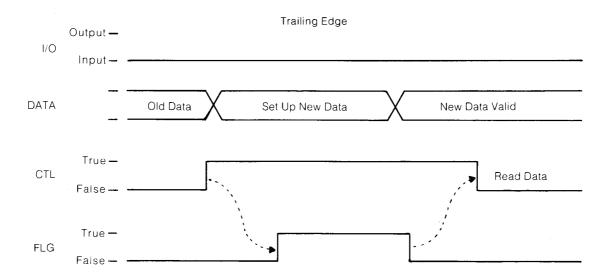

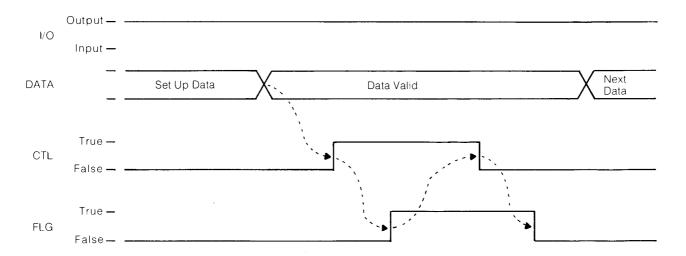

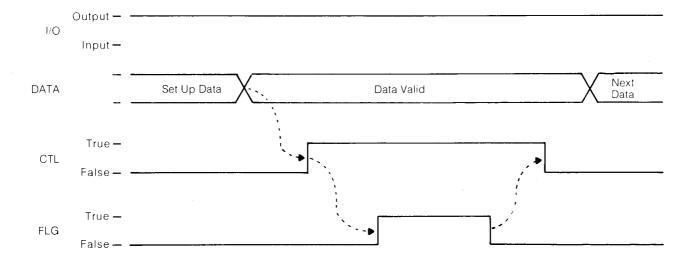

The meanings of the various bits are described next.